Notify me of replies to my comment via email Your email address will not be published. Lowering the clock frequency in the testbench will speed up the simulation.Measuring time in VHDL modules is achieved by counting clock cycles.It also means that the clock period time will be shorter, giving the counter chain even less time to complete. How long a counter you can implement before consuming the entire clock period depends on the FPGA or ASIC architecture and clock speed.Īn increased clock speed means that the counter chain will be longer. If the accumulated length of all the cascaded counters become too long, an error will be produced in the place and route step after compilation. As we increase the length of the counters, we consume of the available time of a clock period. In the real world, the counter value will need some time to propagate from the first bit of the counter to the last one. Note that in simulation, the counter values are updated in zero time at the rising edge of the clock. It’s visible in the first waveform where the 60-second mark on the timeline is slightly before when the Seconds signal wraps to 0. The timer time is slightly offset from simulation time because of the reset of the module at the beginning of the simulation. When changing the time unit from ns to seconds, minute, and hours, we could see that the timer was indeed working in real-time. We right-clicked the timeline in the waveform and selected “Grid, Timeline & Cursor Control”. Such adaptations are sometimes necessary to allow us to simulate a design. If we had left it at 100 MHz, the simulation would have taken days. Fifty hours is a really long simulation, and therefore we had to lower the clock frequency in the testbench to 10 Hz. To run a 50 hour simulation we gave the command run 50 hr in the ModelSim console. The waveform zoomed in on the Hours signal: The waveform zoomed in on the Minutes signal:

The waveform zoomed in on the Seconds signal: Generic map(ClockFrequencyHz => ClockFrequencyHz) We're slowing down the clock to speed up simulation timeĬonstant ClockFrequencyHz : integer := 10 - 10 HzĬonstant ClockPeriod : time := 1000 ms / ClockFrequencyHz

Timer clock with seconds how to#

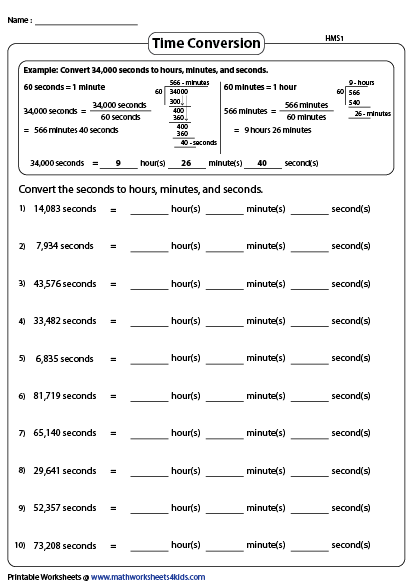

In this video tutorial we will learn how to create a timer module in VHDL: But it will also react slower because the chain of events becomes longer. We are limited by the available physical resources in the underlying technology as well as the length of the counter versus the clock frequency.Īs the length of the counters increase, obviously it consumes more resources. We can continue this approach for counting days, weeks, and months too. Similarly, we can create an Hours counter for counting hours, incrementing when 60 minutes have passed. To count minutes, we can implement another Minutes counter which increments when 60 seconds have passed. When this counter reaches the value of the clock frequency, 100 million for example, we know that a second has passed and it’s time to increment another counter. To count seconds in VHDL, we can implement a counter that counts the number of clock periods which passes. This blog post is part of the Basic VHDL Tutorials series.

Therefore, if we know that the clock frequency is 100 MHz, we can measure one second by counting a hundred million clock cycles. Every digital design has access to a clock signal which oscillates at a fixed, known frequency. The answer is simply counting clock cycles. So how can we keep track of time in a design module? That only works in simulation because we can’t just tell the electrons in a circuit to pause for a given time. But what about production modules? The wait for statement cannot be used for that. In earlier tutorials we have used the wait for statement to delay time in simulation.

0 kommentar(er)

0 kommentar(er)